# The x86 VM System

- Topics

- Hardware support for virtual memory

- X86 (lots of helpful hardware)

- Learning Objectives:

- Explain what MMU hardware has to do

- Describe the x86 MMU support

# A Mapping Table

Conceptually, we need a map from triples to physical addresses (or faults)

(VA, access, privilege) => (PA/fault)

- While we might imagine storing a mapping for every byte in the virtual address space, that would get large pretty rapidly!

- Instead, let's divide memory into fixed-size units called pages.

- We'll store one mapping for each page.

- On the x86, pages are 4 KB.

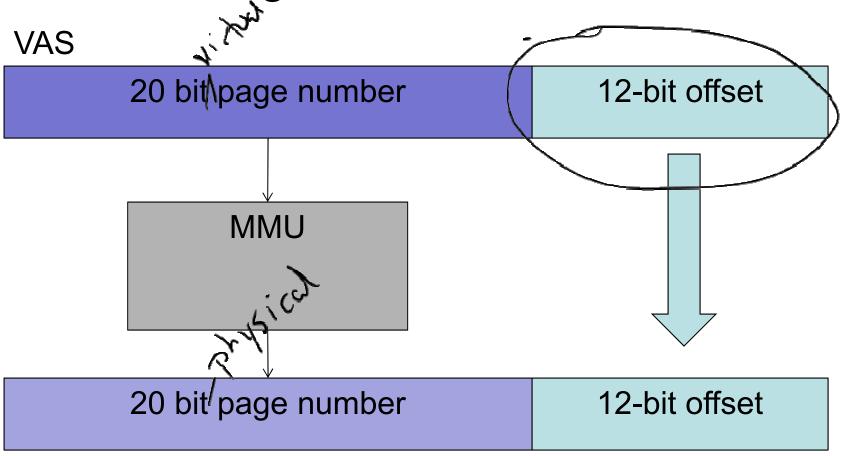

# Dividing the bits in an address

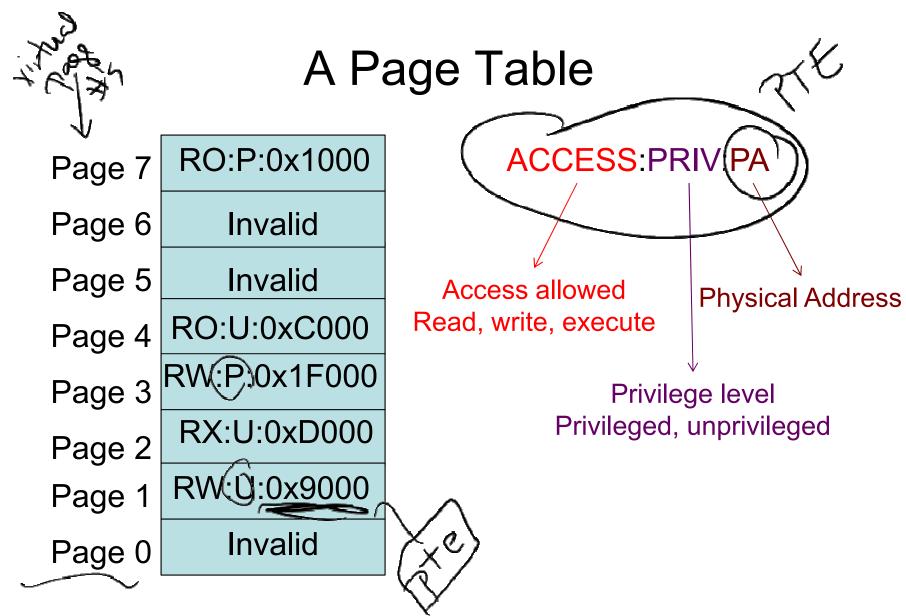

# A Page Table

RO:P:0x1000 Page 7 Page 6 Invalid Page 5 Invalid RO:U:0xC000 Page 4 Page 3 RX:U:0xD000 Page 2 Page 1 Invalid Page 0

Let's translate an address!

A user process tries to read address 0x1234  $\sqrt{3}$   $\sqrt{3}$

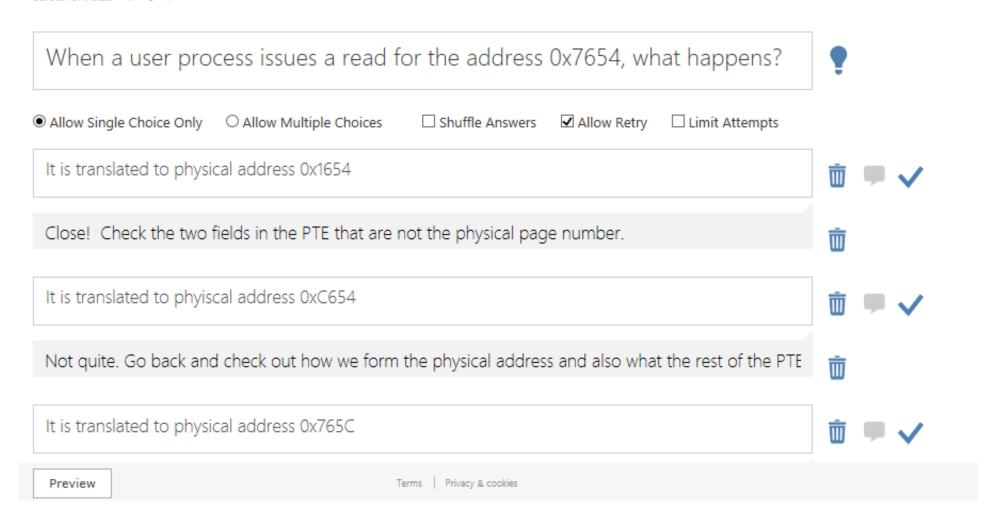

When a user process tries to perform a write to address 0x1230, what happens? Allow Single Choice Only O Allow Multiple Choices ☐ Shuffle Answers ✓ Allow Retry ☐ Limit Attempts It writes to physical address 0x9230 Correct! It writes to physical address 0x1239 Not quite! Go back and check how we construct the phyiscal address. It writes to physical address 0x90000230 Terms | Privacy & cookies Preview

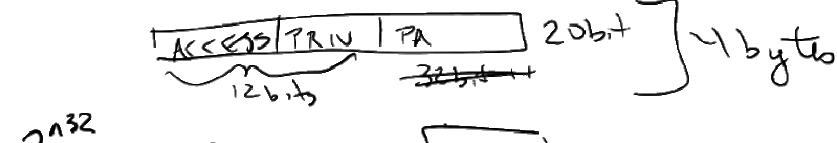

# How big are page tables?

- So, let's see how large our page tables are:

- How many 4 KB pages are there in a 32-bit address space?

$$\frac{2^{n^{32}}}{2^{n^{12}}} = 2^{20} = 1 \text{ M} \implies \text{MB}$$

# Intel x86 VM System

- The Intel x86 Virtual Memory Architecture is a reflection of many major revisions that have occurred over various generations of Intel microprocessors.

- While this makes the system a bit more complicated than some others, it is the most widely used platform today, so understanding it will serve you well.

- Note:

- This presentation does not cover x86 in its full glory.

- We cover it sufficiently so that you can tackle assignment 6

and so that should you ever need to dig into the details, they

will make sense.

# X86 Historical Summary

|             | Introduced | N Instr | Phys. Mem | VAS size |

|-------------|------------|---------|-----------|----------|

| 8008        | 1972       | 66      | 16 KB     | None     |

| 8080        | 1974       | 111     | 64 KB     | None     |

| 8086        | 1978       | 133     | 1 MB      | None     |

| 8088        | 1981       | 133     | 1 MB      | None     |

| 80286       | 1982       | 169     | 16 MB     | 16 MB    |

| 80386       | 1985       | 187     | 4 GB      | 64 TB    |

| 80486       | 1989       | 193     | 4 GB      | 64 TB    |

| Pentium     | 1993       | 198     | 4 GB      | 64 TB    |

| Pentium Pro | 1995       | 234     | 64 GB     | 64 TB    |

| Pentium 4   | 2004       |         | 1 TB      | 16 EB    |

| Core i7     | 2008       |         | 16 TB     | 16 EB    |

P 140 8 1000 00 10

# Manipulating Addresses

### Some handy macros! First, for pages:

```

#define PAGESHIFT 12

#define PAGESIZE (1 << PAGESHIFT)

#define PAGEOFFMASK (PAGESIZE - 1)

#define PAGENUMBER(VA) ((uintptr_t)VA >> PAGESHIFT)

```

#### Next for 2-level page tables:

# Reading Addresses

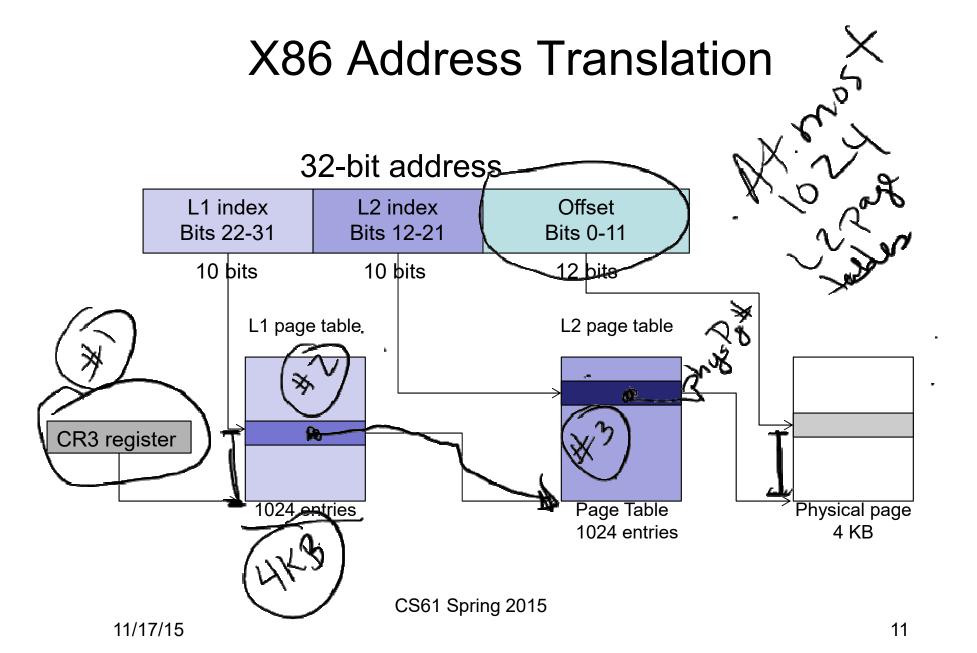

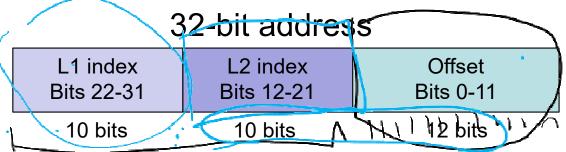

32-bit address

| L1 index   | L2 index   | Offset    |   |

|------------|------------|-----------|---|

| Bits 22-31 | Bits 12-21 | Bits 0-11 |   |

| 10 bits    | 10 bits 5  | 12 bits   | 3 |

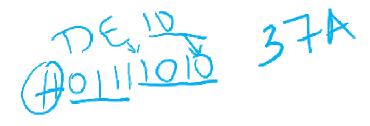

- Let's practice extracting fields from hex addresses.

- How many hex digits for the offset?

- How many for the L2 index?

- How many for the L1 index?

- 0xDEADBEEF

- Offset = Oxker

- L2 Index = > √2 Dt

- L1 Index = 0.37 A

### Wrapping Up

- Page tables are the data structure that maps from virtual addresses to physical addresses.

- The x86 implements 2-level page tables to conserve memory.

- While a complete flat page table would require 4 MB of memory, a tiny process can make do with far less using 2-level page tables:

- 1 L1 page table (4 KB)

- 1 L2 page table (4 KB)

- Total: 8 KB